For the creators of technology

www.electronics-eetimes.com

**HES** europe

June 2016

# IR-based ToF for lightweight 3D mapping

Special Focus: Displays & Projectors Executive Interview: Nantero's CEO Greg Schmergel

out What's New! Digikey.com/new IMMEDIATE SHIPMENT FROM THE WORLD'S LARGEST SELECTION OF ELECTRONIC COMPONENTS™

#

.....

11111

UÂU,

III

:0

#### FIND CONTACT AND ORDERING INFORMATION FOR YOUR REGION AT DIGIKEY.COM/EUROP

4.8 MILLION PARTS ONLINE

SHIPPING

. III III

650+ INDUSTRY-LEADING SUPPLIERS

100% AUTHORIZED DISTRIBUTOR

ELECTRONICS

0

l

i a win

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2016 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

#### **JUNE 2016**

# CONTENTS

#### 4 & 49: OPINION

#### **Uncommon Market:**

Toward OLED-controlled live neural networks Last Word: The only two things that matter for digital companies in China

#### 26 - 31: DISPLAYS & PROJECTORS

32K OLED resolution in demand for commercially acceptable flexible holographic smartphones, says Canadian researcher.

#### 6 - 25: NEWS & TECHNOLOGY

Nanotube-based NRAMs taking over the world soon Founded in 2001, Nantero has come a long way and is now confident it will take a big chunk out of the \$85+ billion memory market.

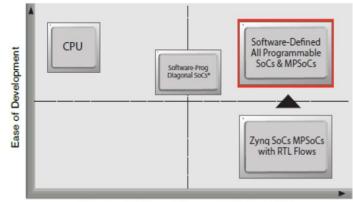

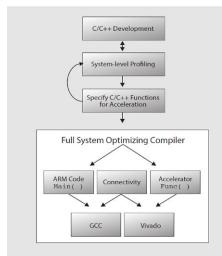

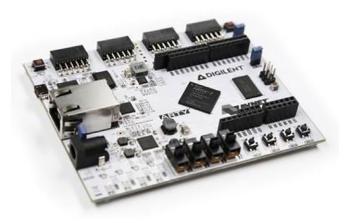

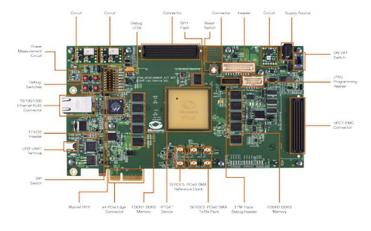

#### 32 - 39: FPGA & DSP

Head of engineering systems at E2V, Adam Taylor reviews 10 interesting FPGA development boards to be used across a number of different applications.

#### 40 - 42: EXOTIC & 2D MATERIALS

Diamonds may soon be the semiconductor industry's "best friend", according to startup Akhan Semiconductor which hopes to roll out the world's first CMOS-compatible diamond semiconductors.

#### **46:** READER OFFER

This month, Pico Technology is giving away three PicoScope 2208B 100MHz Mixed Signal deepmemory Oscilloscopes (MSO), worth 859 Euros each, for EETimes Europe's readers to win.

**50:** DISTRIBUTION CORNER

# **UNCOMMON MARKET**

# Toward OLED-controlled live neural networks

#### By Julien Happich

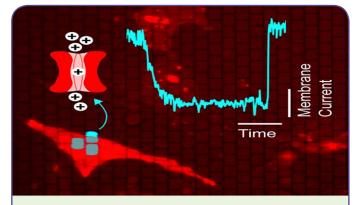

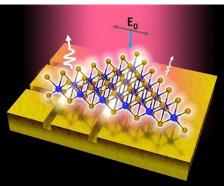

n a paper titled "Arrays of microscopic organic LEDs for high-resolution optogenetics" published in the Advance Sciences journal, scientists at the University of St Andrews detail how they leverage very fine pixel pitch OLEDs in place of a Petri dish to individually trigger living cells and observe their electric activity.

Working with Dr Gareth Miles from the School of Psychology and Neuroscience, Professor Gather and his team used OLEDs as a substrate to manipulate individual, live cells from a human embryonic kidney cell line that were tweaked to produce a lightsensitive protein.

Upon exposure to blue OLED light from pixels directly underneath the cell, the researchers stimulated the electric activity of individual targeted cells, while neighbouring cells remained in the dark and stayed inactive.

The real first here, was that the researchers used a  $20mm^2$  OLED microarray (from Fraunhofer FEP, based on a CMOS backplane featuring 230,000 individually addressable pixels) with  $6 \times 9\mu m^2$  pixels, smaller than the actual cells under study. This enabled the team to optically stimulate not only discrete cells but also different parts of a given cell.

To ensure the shortest optical path (from the OLED pixels used as a substrate) to the cells under study while protecting the OLED active layers, the team only applied a 1.5µm thin-film encapsulation barrier (three layers of  $Al_2O_3$  and two layers of polymer), which they had reported, was enough to keep the OLED functional over several days without noticeable degradation even when fully immersed into a salt buffer solution.

The microarray was then bonded to a flexible flat cable that connects to a custom HDMI driver interface.

In their experimental setup, the team used a standard cell line to test their approach, with a micro-electrode placed

manually to collect the electric response from a given cell. By lighting discrete OLED pixels underneath the modified photo-switchable cells, the researchers were able to switch the cell's membrane potential conductivity states, testing different ion channel activation and deactivation kinetics.

Depending on the cells used, these ranged from 1ms for activation and 21ms for deactivation to bi-stable switching characteristics (the conductive channel being opened or closed by different wavelength exposures). In fact, the emission spectrum of the OLEDs was tuned to match the spectral response of the cells under study. Time

electrodes, recognized Gather in an interview with EETimes Europe, but the professor regarded this OLED-based experiment as only a first step.

"The next step would be to laminate optical or electrical sensors so that when actuator cells start to fire, we could detect the cells' response and interactions across full networks" he said, hinting at the study of neuronal networks.

"As soon as you can have a parallel readout, you can probe one cell and see how it can be excited by other cells".

In fact, not only this OLED-approach could be used to study neural networks, it could even be used to actively tweak such networks, playing on different ion channel activation and deactivation kinetics.

"Rather than having a probe on one neuron, with mechanically flexible micro-OLEDs, you could envisage bio-implants in real brains, wrapped around the surface of the brain", Gather said, adding that with a closed loop and learning algorithms,

The OLED microarray with cells adhered on top of the array (not drawn to scale). The microarray is connected to a high-definition multimedia interface (HDMI) driver with a flexible connector. Each pixel of the array can be turned on and off by the driver and the CMOS backplane. Lightinduced changes in cell membrane current are measured with a patch clamp electrode (voltage clamp mode, whole-cell configuration). The cross section on the right shows the layer structure of the OLED array.

> brain, say to silence the parts that are causing an epileptic seizure", Gather concluded.

you could probe parts of the brain and try to correlate all firing actions, advancing knowledge of the neuronal dysfunction that underlies devastating neurodegenerative conditions such as Alzheimer's Disease, Parkinson's Disease and Motor Neurone Disease.

Today, such studies are performed with bulkier micro-electrodes.

"Ultimately, you could dynamically control parts of the using an epileptic sei

Probing dozens or even thousands of cells in parallel would quickly become tedious if only relying on individually placed

4 Electronic Engineering Times Europe June 2016

# If your 5G idea works here...

# Autonomous vehicles navigating through traffic. Hands free.

Soon it will be reality. A world connected as never before. Always available. Low latency. Ultra reliable. That's the promise of 5G. New spectrum. New waveforms. Millimeterwaves. More. Keysight offers the world's first 5G simulation, design and test environment able to emulate your realworld 5G wireless thesis. With deep expertise to help you navigate 5G risk and complexity. So you can go from 5G ideas to 5G reality faster.

#### HARDWARE + SOFTWARE + PEOPLE = 5G INSIGHTS

Unlocking Measurement Insights

© Keysight Technologies, Inc. 2016

# **Globalfoundries at work on next-gen FDSOI process**

By Peter Clarke

he 22FDX fully-depleted silicon-oninsulator (FDSOI) process developed by Globalfoundries Inc. (Santa Clara, Calif.) is on track to debut later this year and the company is working on the followon process, according to chief technology officer Gary Patton.

Globalfoundries claims its 22FDX platform, four processes with different optimi-

zations, can deliver FinFET performance and energy efficiency at a cost comparable with planar 28nm CMOS. The ability to perform back-biasing provides the opportunity to dynamically change the operation of transistors from performance to minimal leakage.

However, FinFET production remains the mainstream option for leading edge ICs that is best supported by foundries, including Globalfoundries, and by IP developers. In addition Samsung's foundry is also offering a 28nm FDSOI process.

Patton, previously a career-long IBM researcher, was brought in to Globalfoundries when the foundry acquired IBM's semiconductor operations.

"We looked at both FinFET and FDSOI is perfectly suited for the mobile space," Patton told EE Times Europe on the sidelines of the IMEC Technology Forum held in Brussels this week. "The work started in Malta (New York) and has transferred to Dresden. The yields are ahead of schedule and the focus is on getting design IP built up."

Globalfoundries is working with a company called Invecas Inc. to develop foundation IP for its 14nm FinFET and 22nm FDSOI manufacturing processes. The schedule for 22FDX has Globalfoundries starting risk production for customers late in 2016 with volume manufacturing arriving in 2017.

Patton made the point that FinFET processes with their high

#### with moving to another planar process, such as FDSOI," he said. However the FDSOI process - originally research by IBM and then championed by STMicroelectronics and now Globalfoundries and Samsung – has had a difficult gestation. It is four years since

With the possibility of potential design wins for FDSOI going to 16nm and 10nm FinFET processes a lack of road-map could be seen as a disadvantage. Modern design involves the migration of larges amounts of proprietary and third-party IP cores and therefore continuity of process is significant.

"We have a next generation fully depleted process that is underway in Malta," Patton said without confirming a nominal node name. The labelling of nodes with a minimum dimension is largely moot in the modern era. Upcoming 10nm and 7nm nodes from TSMC will have minimum feature sizes of about 20 and 14nm respectively and be produced on 32nm or 36nm pitch.

# FDSOI is driving ST's automotive businesses

#### By Peter Clarke

he fully-depleted silicon-on-insulator (FDSOI) chip manufacturing process championed by STMicroelectronics has become almost the default choice for digital manufacturing within the automotive and discrete group (ADG) business unit at ST, according that group's senior executive.

And that emphasis on FDSOI will continue through the manufacture of automotive microcontrollers in 28nm FDSOI, said Marco Monti executive vice president responsible for the ADG business unit.

Monti said that while ST's most advanced microcontrollers are on 40nm CMOS the next generation will be on 28nm FDSOI with some sort of non-volatile memory possibly based on phasechange memory. "The use of FDSOI in MCUs at ST is driven by automotive," said Monti. Rival European chip company and automotive supplier NXP Semiconductors is also expected to develop MCUs based on 28nm FDSOI.

One particular automotive IC development – Mobileye's EyeQ5 - is not targeting FDSOI, but this is because it is a very long-term and high performance project that will be unlikely to see silicon before the end of the decade, Monti told EE Times Europe. In the near- to medium-term, with digital electronics in automotive applications growing rapidly, FDSOI is key to ST's strategy, he said.

"EveQ5 is a very long term development and very complex; for full level-4 autonomous driving. It will reach production in 2022 and volume in 2025 but all the rest in ST automotive is driven by FDSOI technology. The EyeQ4 vision processor that will enter production in 2017 is on FDSOI. That is targeting level-2/level-3 autonomy," said Monti. The development team at ST has just won a special award from customer Mobileye because the EyeQ4 reached higher-than-expected performance levels, Monti added.

There are numerous other examples of FDSOI chips in development, Monti said.

These include: a next-generation Sirius XM satellite radio chip in 28nm FDSOI that will sample this year; ST's car-communications activity with Israeli customer Autotalks Ltd. "Automotive-grade Wi-Fi is on 28nm FDSOI; all the processors for automotive entertainment are going on FDSOI, our telematics processor. And we have a specialization in 28nm FDSOI for RF to make 77GHz radar for ADAS applications," Monti added.

"FDSOI is not just a manufacturing node for us. It's a whole cluster of technologies for all things in the car."

drive current capability are well suited to driving signal lines across large chips and where sustained performance is required. However, for smaller chips and chips where power consumption is key then FDSOI is a better option. Patton also makes the point that FinFETs have a quantized drive regime where a developer must choose between 1, 2 or more fins,

which is not suited to analog or RF signal.

But although Globalfoundries has been extolling the virtues of 22FDX for analog and the RF in the Internet of Things (IoT) Patton makes the point that the process also addresses digital requirements. "There's a ton of digital business in mobile sitting at 65nm, 40nm. And the cost of migrating that to FinFET is high compared

an initial deal between STMicroelectronics and Globalfoundries to produce FDSOI in volume at the Dresden wafer fab.

# Where your innovation begins:

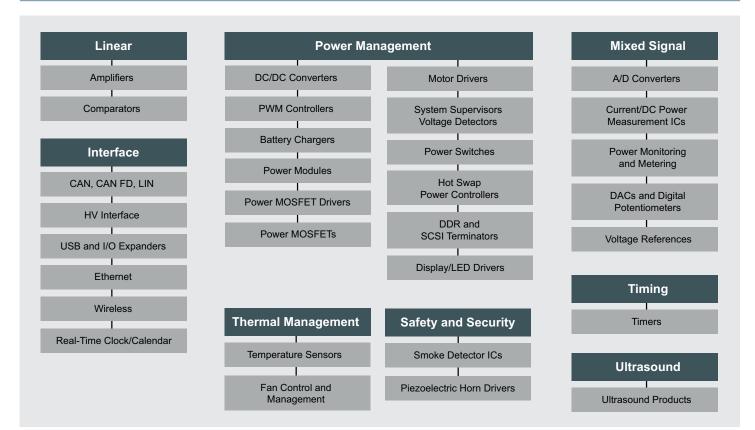

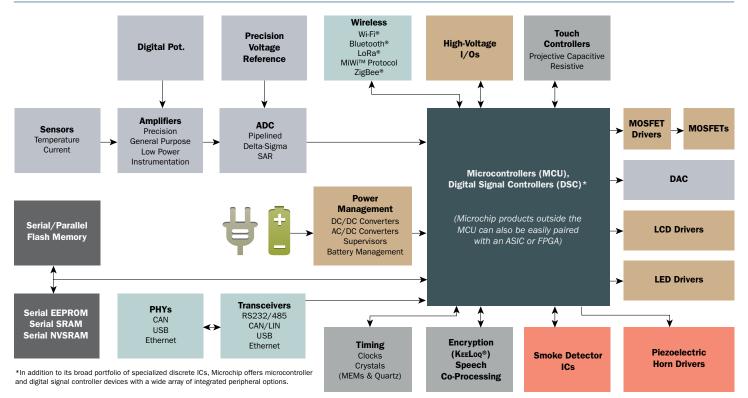

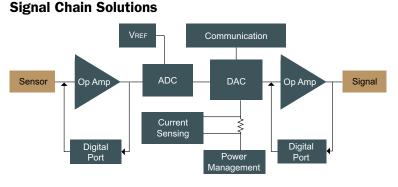

## **Microchip's European MASTERs 2016**

19th - 21st September 2016, HTW - Berlin, Germany

# Benefit from up to 3 days of learning on new technologies that can realise your designs for future products. Be one of the first of our 35,000 clients in Europe to take advantage of this technical seminar.

#### Innovative design engineers are requested to join us to discover how to:

- Reduce your time to market

- Address new market opportunities

- Lower your design cost

- Manage your development risk

#### By selecting from 70+ classes covering all of our innovative technologies

Register Today www.microchip.com/eumasters

- ▶ Internet of Things / The Cloud

- Motor Control

- Touch and Gesture Technology

- USB

- Bluetooth<sup>®</sup>

- ▶ Wi-Fi®

#### **Event Pricing**

- Early Bird Special: EUR 441 (exc VAT)

valid until 18th June 2016

- Regular Price: EUR 490 (exc VAT)

- Analog & Mixed Signal

- Audio

- Power Supply & Power Conversion

- Design Techniques

- ... And more!

#### **Discounts available for:**

- Microchip Design Partners

- Groups

- Microchip Academic Partners

The Microchip name and logo is a registered trademark of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are the property of their respective companies © 2016 Microchip Technology Inc. All rights reserved. MEC2076Eng/05.16

# **Google designing AI processors**

#### By Rick Merritt

oogle has developed its own accelerator chips for artificial intelligence it calls tensor processing units (TPUs) after the open source TensorFlow algorithms it released last year. The news was the big surprise saved for the end of a two-hour keynote at the search giant's annual Google IO event in the heart of Silicon Valley.

"We have started building tensor processing units...TPUs are an order of magnitude higher performance per Watt than commercial FPGAs and GPUs, they powered the AlphaGo system," said Sundar Pichai, Google's chief executive, citing the Google computer that beat a human Go champion.

The accelerators have been running in Google's data centers for more than a year, according to a blog by Norm Jouppi, a distinguished hardware engineer at Google. "TPUs already power many applications at Google, including RankBrain, used to improve the relevancy of search results and Street View, to

improve the accuracy and quality of our maps and navigation," he said.

The chips ride a module that plugs into a hard drive slot on server racks. Engineers had them running just 22 days after they tested first silicon said Jouppi, who previously helped design servers and processors at Hewlett Packard and Digital Equipment.

Given the nature of Al algorithms, "the chip [can] be more tolerant of reduced computational precision, which means it requires fewer transistors per operation...[and thus] can squeeze [in] more operations per second," he said.

The project started several years ago. Google has been hiring engineers with semiconductor expertise for some time. However, it managed to keep secret what they were working on, despite the fact the chips are already running in systems. To date, Microsoft and Baidu have opted to use FPGA accelerators for their cloud services. Facebook designed a GPU accelerator and made it open source.

The algorithms caught fire when they showed about three years ago the ability to recognize images as well or better than humans. Google's demonstration at playing Go was another key milestone given the complexity of the game.

In one game of the match, "move 37 was the most beautiful move due to its creativity," said Pichai. "We normally don't associate computers with making creative choices, so this is a significant achievement in AI, he said, noting the human Go champion has since used the move in other games.

Google released no details about the new chips. Pichai said the the search giant's TensorFlow algorithms which he said has one become of the most popular projects on GitHub.

Don't expect Google to provide merchant versions of the

chips. Access to TPU hardware "will be one of biggest differentiators for the Google Cloud Platform," he added.

Pichai gave examples of how Google is using Al to make robotic arms more accurate. It is also working on an expert system to help prevent diabetic blindness through early diagnosis.

"We live in an extraordinary period for computing...The real test is whether humans can achieve more with AI assisting them so things previously thought impossible may become possible," he concluded.

Google claimed the TPUs are three process generations ahead of the competition, said Kevin Krewell, senior analyst with Tirias Research. "The TPUs are "likely optimized for a specific math precision possibly 16-bit floating point or even lower precision integer math,"

The TPU fits on a module that plugs into a hard disk slot in a server rack. (Image: Google)

The company is not the first to design an accelerator specifically for AI. Nervana Systems is preparing a cloud service that will be based on its own AI accelerators. Movidius has its own merchant chip for embedded applications, and recently announced plans for a high-end version.

The news comes amid a broad debate in the computing industry over the last few years about how best to accelerate emerging AI algorithms such as convolutional neural networks.

#### Krewell said.

"It seems the TPU is focused on the inference part of CNN and not the training side," Krewell said. "Inference only requires less complex math and it appears Google has optimized that part of the equation.

"On the training side, the requirements include very larger data sets which the TPU may not be optimized for. In this regard, Nvidia's Pascal/P100 may still be an appealing product for Google," he added.

#### **ARTIFICIAL INTELLIGENCE**

Google Home is a voice-activated assistant coming this fall, similar to Amazon's Echo. (Image: EE Times)

Beyond the surprise news of the TPUs, the annual Google IO was in many ways about the search giant playing catch up with rivals Amazon, Apple and Facebook's Oculus in areas from virtual reality to smart homes and watches.

In VR, Google will make its own hardware, and has announced a reference design for VR headsets and controllers others cane make using extensions in Android N. A beta version of the operating system is available now with the first VR hardware using it coming in the fall.

Google calls its approach to VR Daydream and worked with handset and chip vendors to define a specification for smartphones that are Daydream-ready. Phones compliant with the spec are expected this fall from the likes of HTC, Huawei, LG, Samsung and Xiaomi.

Android N will support VR latencies as low as 20 milliseconds, Google claimed. The company is working with game and movie developers to release VR titles for Android N. It will also support Daydream VR in its own services including new and existing YouTube videos, Google Photos and Street View in Google Maps.

Overall, Android N will pack 250 new features, including support for Vulkan, the graphics API also used by desktops and game consoles. It sports file-based encryption, and a faster runtime and new JIT compiler to load apps faster while using less memory.

Separately, Google announced it will ship this fall its own voice-based controller called Home, competing with the Amazon Echo. Home will act as a gateway controlling delivery of digital music and video to speakers and TVs. It has its own built-in speakers, links to home devices like Nest thermostats and can process natural language Google search requests.

In addition, Google announced Android Wear 2.0, a version that better mixes and matches data from various applications and is ready for cellular-enabled watches.

Finally, Google also previewed Duo, its answer to Apple's FaceTime video calling app. It uses features in the WebRTC standard to show video of a caller before a user picks up a call and will be available on both Android and iOS this summer.

#### mouser.com

The Newest Products for Your Newest Designs®

# The widest selection of the newest products.

Over **4 Million** products from over **500 manufacturers.**

Authorised distributor of semiconductors and electronic components for design engineers.

# **European battery 'Gigafactory' opens**

By Graham Prophet

MZ GmbH (Karlstein-Großwelzheim, Germany) has opened the first section of what will be Europe's biggest lithium-ion battery factory, labelling it as "Europe's Gigafactory" in an allusion to the Tesla battery plant being built in the western USA). Over the next four years, BMZ plans to more than quadruple production areas in Germany.

With construction taking only a little over a year, BMZ, a developer and producer of intelligent lithium-ion batteries, has now opened up the first two production, logistics and office

buildings in addition to an existing production areas of 7,000 m<sup>2</sup> at the company's present headquarters. In the manufacturing units comprising 4,800 m<sup>2</sup> each, up to 200 million lithium-ion batteries of the most different kind and size with an overall storage capacity of about 15 GWh can be developed, produced and tested every year.

By 2020 four further production, laboratory and office buildings covering a total space of 15,000 m<sup>2</sup> are planned on the new company site of 55,000 m<sup>2</sup>. After the completion of the construction works up to 1,500 BMZ employees will produce 800 million lithium-ion batteries in a range of different sizes annually with an overall storage capacity of 30GWh, from the industrial site in Karlst ein-Großwelzheim alone.

At present the company has around 120,000 m<sup>2</sup> production sites in its own companies in Germany, China, the USA and Poland. Company founder and owner Sven Bauer explains, "The current discussions on subsidies for electric cars often forget that lithium-ion batteries are also used in e-bikes, electrical appliances, gardening tools, energy storage systems, transport vehicles, excavators and so on." The request for maximum mobility stimulates not only the demand for well-known appliances such as vacuum cleaners or drill hammers. With modern lithium-ion batteries numerous new ideas can be realized of which robotic lawn mowers are only one of many examples. The market potential for batterypowered appliances is enormous.

"From our point of view it is most important to commonly build up our own production of lithium-ion cells in Germany, too. That is the only way to reduce the dependency risks on the few,

"Unlike electric cars we are presently undergoing a real demand boom in many of these sectors, and we assume that the demand in these segments will further increase by 15 to 30% annually in the coming years depending on application range. The modular concept of our new ultra-modern factory units enables BMZ to respond even faster and more flexible to this growth scenario as well as specified customer requests in the future."

The setup of Europe's biggest lithium-ion battery factory in Karlstein shows – according to Bauer – how important this technology has become especially for the industry location Germany. The battery expert assumes that by 2020 wireless solutions will dominate the markets; a development that will offer enormous growth opportunities. mainly Asiatic cell producers in the long run," says Bauer. As a first intermediate step, BMZ intends to launch their own extremely efficient cell, which is to be applied in their own as well as customer-related battery systems. The cell, which will be available in prototype form at the end of this year claims 100% higher durability, 68% more performance, 88% more energy, 400% more charging current and up to 60% more capacity compared with usual cells according to the industrial standard 18650.

In 2015, the company, which was founded in 1994, achieved a turnover of some 350 million euros as the largest independent European lithium-ion battery system developer and manufacturer, with more than 1,200 employees worldwide. The 500 million threshold is expected to be broken in 2020 at the latest.

# Stay cool, be MAP

electronica Munich Hall B6 Booth 404

# #coolMAPI WE speed up the future

The WE-MAPI is the world's smallest metal alloy power inductor. It's efficiency is unmatched. Available from stock. Samples free of charge. For further information please visit: www.we-online.com/WE-MAPI

Design your DC/DC converter in **REDEXPERT**, the world's most precise software tool to calculate AC losses.

- highest current ratings

- lowest AC losses in class

- incredibly low DCR

- excellent temperature stability

- innovative design

- lowest EMI radiation

The full WF-MAPI range:

1.6x1.0 2.0x1.0

2.5x0.6

2.5x1.0

2.5x0.8

2.5x1.2 3.0x1.0

3.0x1.2

3.0x1.5

3.0x2.0

4.0x2.0

# **NEWS & TECHNOLOGY**

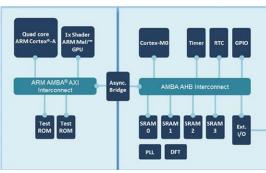

# **ARM describes 10nm test chip**

By Jessica Lipsky

RM announced it taped out a 10nm FinFET test chip in January at TSMC. Chips made in the process will be in handsets by the end of the year, ARM said, describing the node as relatively expensive and focused on lowering power.

The ARM test chip used four of its yet-tobe-disclosed

Artemis cores running at 2.8 GHz, an unknown GPU and memory subsystem among other

components. Unlike previous nodes, the TSMC 10nm process is focused less on pushing performance to the max and more on lowering power consumption, ARM said.

Compared with a Cortex A-72 on TSMC's 16FF+ process, the 10nm SoC operating on the same frequency showed a 0.7%, 11% and 12% improvement in performance depending on the use of overdrive which ARM defines as nominal + 100mV. Eventually, 10nm chips should show a 30% improvement in power consumption compared with its predecessors.

The Artemis core itself appears to be focused mainly on lowering power consumption and size based on ARM's comments about the test chip.

"Artemis is a small core, so you're going to get some architectural benefits in leakage, just as much frequency, better power and smaller," said Ron Moore, vice president of marketing for ARM's physical design group.

"Performance between Artemis and an A-72 are going to be pretty much at the same level."

TSMC has been working closely with ARM on process technology and IP for the past four years. However, ARM also is working with Samsung as its foundry aggressively pushes toward its own 10nm FinFET process.

While Samsung and TSMC race to be the first to market with a 10nm node, Moore isn't concerned about who comes in first. "The fin size is different but I can accomplish the same thing wing Attention both processes " to talk

using Artemis in both processes," he told EE Times.

Jim McGregor, Tirias Research principal analyst, expects Samsung and TSMC to continue to battle it out but also run into some of the same challenges Intel faced when ramping 14nm.

"Both these guys are ramping aggressively with ARM-based products. That really shows the strength of the ARM architecture," McGregor told EE Times. "If you had

to compare process to process, when Intel gets to 10nm they'll probably still have the most aggressive process of any of them, but Intel hasn't shown their ability to be an effective foundry," he said.

Moving to the 10nm node comes with additional costs. Moore said the design cost for developing a physical implementation of 28nm was about \$5.5 million, while 10nm will cost approximately \$32.5 million - a figure initially given by International Business Strategies in August 2015. A 10nm chip requires more iterations, IP, and likely more machine time – all of which is likely to trickle down as additional costs for chip designers and their foundries, he said.

"The early ones in pay for the early development cost. They

Test chip architecture Source: ARM

pay for the high really expensive design tools, they pay the big premiums because they can afford more and because their markets are bigger," said VLSI Research CEO G. Dan Hutcheson. "I think the costto-design argument, to some extent, is a bragging right."

Hutcheson continued that the general design cost for a chip

shouldn't be more than 15% of its sale price, and added that there is a lot of complexity in that design figure. The amount of IP in the ecosystem, the cost of a design team, the capability of design tools and the size of the market all play into that \$32 million figure – which will shrink as 10nm proliferates.

At an analyst event, ARM didn't provide updates on a lowercost alternative, fully-depleted silicon on insulator (FD-SOI), which the company acknowledged as a viable technology during the FD-SOI Symposium last month.

"FD-SOI is still very much a good technology and it is a very power efficient technology," Moore said.

"We do not see the customer adoption and the ecosystem. What you're missing is the LPDDRs, the memory interfaces, the IP kind of stuff," he said. "FD-SOI is probably not being adopted as well as it could because the ecosystem is trailing. I think the foundries that want to do the FD-SOI will have to invest," he added.

One of the challenges of FD-SOI adoption is the analog, RF and high speed interface IP needed to support diverse market segments, Moore told EE Times, pointing to the needs in mobile, enterprise, and embedded/IoT markets.

ARM already ports devices to FD-SOI, Hutchenson noted, though the porting process is tedious. The issue isn't the ARM core but supporting a variety of ecosystems and thousands of

> potential IP. Moore said foundries will need to provide "seed funding" to build out the IP ecosystem for each of market, including porting complex IP from BULK to FD-SOI.

Kelvin Low, Samsung's senior director of foundry marketing, said his company has "substantial IPs" for FD-SOI that have been product tested. A GlobalFoundries' representative said the company will support FD-SOI for SoCs by the second half of 2017.

ARM "We are developing IP [on our 22FDX platform] concurrently with technology development," a Global-Foundries spokesman said.

"Some of them have gone through early silicon validation and others are in various stages of design and silicon validation," he said. "Prototype SoCs are being taped out now using early versions of IPs. A complete set of silicon validated foundation and complex IPs will be available for SoC design start and tapeout, [and] we are on target to support SoC product launch in 2H2017," he added.

"No company has the breadth of the entire ecosystem of IP," Hutcheson told EE Times. "If I were to guess, it's in their advantage to minimize the number of ecosystems they have to support."

bout who comes in first. though though the same thing to core but the same thing to but the same thing to but the same thing to be the same thing to be the same the

Data on total power versus performance of 10nm FinFET test chips compared to 16nm FinFET. Source: ARM

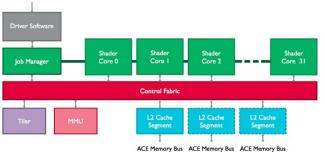

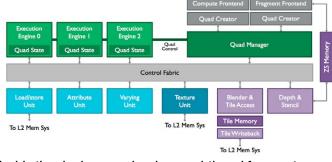

# ARM's Bifrost steps up graphics, bridges to machine learning

#### By Peter Clarke

he Mali-G71 GPU core is ARM's first that follows a new architecture called Bifrost that has been launched providing support for the Vulkan API from the industry-run Khronos Group.

The architecture includes maths capabilities that could be used by other software as part of a heterogeneous system architecture. That could include neural network software but ARM executives stressed that Bifrost is first and foremost an architecture for raster. tilebased graphics processing units (GPUs).

The previous architecture - Midgard - is the shader cores, Source ARM. one that underlies ARM's T-series Mali GPUs and has up to 16 unified shader cores and SIMD [single-instruction multiple data] instruction set architecture. Bifrost supports up to 32 unified shader cores with a scalar ISA, full hardware cache coherency and something called clause execution.

The primary goal, according to Sean Ellis, GPU architect with ARM, was to achieve more performance per square millimetre of silicon and per line of "real-world" shader code. And this has been achieved to tune of about 50 percent through the use of a new scalar, clause-based ISA, with guad-based arithmetic units

Whereas Midgard GPUs use SIMD vectorization Bifrost GPUs will use guad vectorization in which four scalar threads from a 2 by 2 pixel are executed in lock step. Each thread fills one 32-bit lane of the hardware and four threads doing a vec3 FP32 add takes three cycles. In short guad-vectorization is compiler friendly and improves resource utilization.

Clause execution is another refinement that is used to reduce overhead compared with the previous graphics architecture. A "clause" is defined as a sequence of instructions that are self-dependent and without variable latency. Whereas previously temporary registers are used after every instruction under Bifrost an architecturally visible state through temporary registers is only guaranteed after each clause. The back-to-back execution of instructions within a clause allows for aggressive optimization and saves power. Clause boundaries are decided in the compiler, Ellis told journalists and analysts.

When asked if there was specific support within Bifrost for GPU-computing - where the GPU is used to run software to which it may be better suited than the CPU core cluster - ARM

executives said that decisions had been taken to include support for a variety of data types that are not generally used in graphics. These include 8, 16 and 32bit integers as well as 16bit floating point.

The FP16 can be used for some pixel shaders at twice the nominal throughput. Similarly Bifrost supports 64bit floatingpoint precision at half nominal throughput. Meanwhile the integer math and FP16 are useful for

Top level architecture of Bifrost showing up to 32 universal

deep learning applications, Ellis said. ARM has never

been particularly keen on the raytracing approach to graphics rendering, which is a completely different approach to tile-based rendering. Indeed it acquired Geomerics Ltd. in 2013, a leader

in software engines for lighting effects in software games. Ellis told *EE Times Europe*: "Ray tracing is not explicitly excluded [from Bifrost]. But we can

do lighting, shadowing, glare effects in other ways."

#### Vulkan

Vulkan is a 3D graphics API for the next 20 years, said Jem Davies, ARM Fellow and vice president of technology for media processing. "Vulkan 1.0 was released in February with unprecedented support. It is available on the desktop in Windows and Linux and will be supported in upcoming N generation of the Android operating system.

"In 2014 the traditional 3D APIs were in trouble with unpredictable performance and the emergence of proprietary efforts such as Mantle, DX12." So a crash effort in a next-generation OpenGL initiative was launched. AMD donated its Mantle technoloav.

The major result is that under Vulkan more responsibility is given to the application making for a lower overhead driver. The driver handles memory allocation, resources, and thread management to generate command buffers. Vulkan is multithread and multicore friendly and error checking is opt-in, said Davies. "Vulkan is a great fit for mobile graphics architectures because there is no wasted effort trying to look like a desktop GPU," he added.

ARM already has Vulkan drivers for T880/T860/T760 and the Mali-G71 driver is ready and awaiting silicon.

And progress continues with Vulkan 1.1 expected soon, said Davies. "I think we will see features added to further reduce power and bandwidth. Thermal throttling of processors is a big

deal." Davies said that texture compression helps in this regard and AFBC [ARM Frame Buffer Compression] is becoming commonly supported but when asked if AFBC would be standardized within Vulkan 1.1 said: "We would welcome AFBC being established as standard but it's unlikelv."

However, Vulkan 1.1 could also include further developments to support GPU-compute. "The GPUcompute voice is getting louder as time goes on," Davies said.

Inside the shader core showing quad-thread fragment management and execution engines. Source: ARM.

# **NEWS & TECHNOLOGY**

# **'Internet of Sensors' project kicks off in Europe**

#### By Peter Clarke

oSense, a European pilot line project has kicked off in Dresden, Germany at the site of project leader Infineon Technologies AG.

loSense is a three-year project with 33 partners from six countries collaborating on R&D across the value chain for

sensors and a budget of €65 million (about \$70 million). Although there are numerous academic and research institute partners the main commercial participants are Infineon, AMS, Philips Lighting and Siemens.

The European Commission is providing  $\in$ 14.7 million (about \$16.5 million) and the German state of Saxony and the German Federal Ministry of Education and Research (BMBF) will contribute  $\in$ 5.2 million (about \$5.8 million).

The name derives from Internet of Sensors and is intended to support the creation of three pilot lines (two front-end and one back-end) for the production of both discrete and integrated sensor systems.

The project has been divided into 7 technical work packages with a further two focused on the management of the project and standardization and dissemination of the results. "Sensor solutions from Infineon in cars make a major

FLOWER FERENCE OF RUCE THE FLOWER FERENCE OF RUC

contribution to improving road safety," said Reinhard Ploss, CEO of Infineon, in a statement. "With an increasingly networked world and the Internet of Things, the demand for such sensor solutions will see a dramatic rise. In addition, sensors are increasingly employed in smartphones and lifestyle products. We will benefit from this market growth through new sensor technologies and competitive production methods."

AG is set to lead another European research project that will begin this month. Semi40 will focus on manufacturing power semiconductors according to Industry 4.0 requirements.

# Machine-learning radars may be coming to automotive

#### By Peter Clarke

he IMEC research institute (Heverlee, Belgium) plans to make future sensors, and specifically radar sensors, devices that extract useful information locally and even become learning machines.

IMEC is already working with automotive radar market leader Infineon Technologies AG at 79GHz in 28nm CMOS. Now it wants to go to a yet smaller wavelength and add machine learning to the back end of its sensors said Wim van Thillo, program director for perceptive systems at IMEC, speaking at the IMEC Technology Forum.

Van Thillo said his group is already working on a 140GHz chip. At this frequency the wavelength is 2.2mm and his group is aiming for more than 4GHz of bandwidth from a chip measuring 1 square millimeter, he added.

The advantages will include higher distance and angular resolution at lower power in a much smaller system size with the radar able to include the antenna-

on-chip. In addition to angle and distance the radar is able to provide speed information via a mini-doppler effect. The use of multiple antennas integrated on to the chip will result in enhanced Doppler resolution and a better depth resolution.

The signal processing that will be needed to extract speed information is likely to be taken further with the use of algorithms for pattern recognition and automatic learning. As a result Van Thillo envisages a time when the radar will be able to recognize and distinguish the signature of pedestrians, bicycles and cars from their mini-Doppler signatures.

Massimiliano Maranella, program manager for millimeterwave perceptive systems, said that 28nm CMOS is being used again and that in simulation at least the signals look good enough to use. However, it acknowledged that a 28nm CMOS platform would not be suitable for long-range (300m) automotive radar.

A complication is that the plastics used in bumpers and metallic paints tend to absorb the energy at 140GHz, Maranella said.

However, while the frequency may be used in shorter-range gesture recognizing systems the learning can be extended across a broader set of perceptive systems including automotive.

For example, such maa sensor fusion system that

chine learning radars will be part of a sensor fusion system that combines visible and radar to make the best identification. But one of the big advantages of the coming connected-car is that vehicles will be able to benefit from "fleet-learning" Van Thillo said. So cars will be learning how to identify and react to hazards far faster than an individual vehicle would.

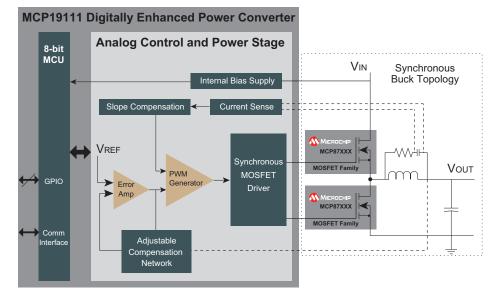

# High-Performance ICs Simplify Your Sophisticated Digital Power Designs

The dsPIC33EP "GS" family delivers the performance needed to implement more sophisticated non-linear, predictive and adaptive control algorithms at higher switching frequencies. These advanced algorithms enable power supply designs that are more energy efficient and have better power supply specifications.

- ▶ Higher performance enables more sophisticated algorithms

- More integration

- Live update capability

- ▶ Smaller footprint with 4 × 4 mm package saves board space

- Easier digital power design

iiid

MPLAB<sup>®</sup> Starter Kit for Digital Power (DM320017-2)

www.microchip.com/dsPIC33EP-GS

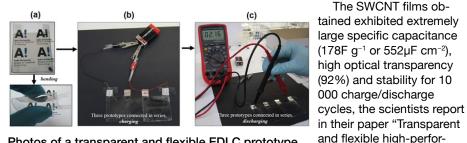

## **CNTs & photonics to break solar conversion theoretical limits**

#### By Julien Happich

n their Nature Energy paper "Enhanced photovoltaic energy conversion using thermally based spectral shaping", MIT researchers demonstrate how they were able to boost a traditional photovoltaic cell conversion efficiency by converting the broadband sunlight to a narrowband thermal radiation precisely tuned for the photovoltaic cell at hand.

Relying on the broadband absorption of vertically grown carbon nanotubes (CNTs) integrated with a one-dimensional photonic crystal selective emitter and paired with a tandem plasma–interference optical filter, the researchers managed to

MIT's thermophotovoltaic assembly showing a circular layer of ultra-black CNTs covering a onedimensional photonic crystal, over an optical filter (green) cover the standard solar cell. Courtesy, MIT's researchers.

suppress 80% of unconvertible photons, achieving a solar-toelectrical conversion rate that exceeded the performance of the photovoltaic cell alone.

Their research also established that the resulting device could operate more efficiently while reducing the heat generation rates in the photovoltaic cell by a factor of two for a given output power density.

With solar thermophotovoltaics, lead author MIT doctoral student David Bierman sees a new energy harvesting route that could help traditional solar cells break their energy conversion theoretical limits.

Instead of dissipating unusable solar energy as heat in the solar cell, thermophotovoltaics devices first absorb all of the energy and heat through an intermediate component (the ultrablack CNT layer on top of a one-dimensional photonic crystal seen on the top of the thermophotovoltaic assembly).

Reaching high temperatures (1,000 degrees Celsius in their experiment), these added layers are tuned to only emit thermal

radiation at the optimal wavelengths of light for the solar cell to operate at peak efficiency.

By pairing conventional solar cells with these custom-designed emissive layers, one could more than double the theoretical limit of efficiency, potentially making it possible to deliver twice as much power from a given area of panels, expects Bierman.

One implementation could be to use a conventional solar-concentrating system, with lenses or mirrors that focus the sunlight, to maintain the high temperature.

An advanced optical filter would let through all the desired wavelengths of light to the PV cell, while

reflecting back any unwanted wavelengths. Those reflected wavelengths would then get re-absorbed, helping to maintain the heat of the photonic crystal.

Because the photonic device produces emissions based on heat rather than light, such a thermophotovoltaic device would be unaffected by brief changes in the environment, such as clouds passing in front of the sun, as the researchers demonstrated.

It could even be coupled with a thermal storage system to make use of solar power on an around-the-clock basis. In addition, because of the way the system harnesses energy that would otherwise be wasted as heat, it can reduce excessive heat generation that can damage some solar-concentrating systems.

The researchers are now looking at implementing larger versions of their small, laboratory-scale experimental unit, trying to find new ways of manufacturing such systems economically.

# 3-bits per cell for IBM's phase-change memory

#### By Julien Happich

ive years after they had published their first results proving the viability of a 2-bit per cell phase-change memory (PCM), scientists at IBM Research

have managed to push their coding scheme and design to store 3 bits of data per cell.

The researchers first demonstrated reliable storage and moderate data retention of 2 bits/cell PCM, on a 64 k cell array, from room temperature (around 30°C) to 80°C and after 1 million SET/ RESET endurance cycles. Under similar operating conditions, they then dem-

onstrated the feasibility of 3 bits/cell PCM (eight levels of data encoding), with a chip consisting of a  $2\times 2$  Mcell array with a 4-bank interleaved architecture.

The memory array size is 2×1000µm×800µm and the PCM cells are based on doped-chalcogenide alloy, they were inte-

grated into the prototype chip serving as a characterization vehicle in 90nm CMOS baseline technology.

"Reaching three bits per cell is a significant milestone because at this density the cost of PCM will be significantly less than DRAM and closer to flash", said Dr. Haris Pozidis, manager of non-volatile memory research at IBM Research and one of the authors of the paper presented at the IEEE International Memory Workshop in Paris.

The multi-bit storage capability relies on a set of driftimmune cell-state metrics and drift-tolerant coding and detection schemes.

trapped within the epitaxy layers

With this hybrid architecture,

proximity to the multiple quantum

wells (MQWs) of the active area.

the QD emitters are placed in close

the out-coupling efficiency between

MQWs and QDs, simultaneously al-

lowing for a non-radiative resonant

energy transfer between the MQWs

and the QDs and near-field radia-

tive coupling of trapped (guided)

modes in the LED to the emitters.

symmetrical far-field beam shape,

the 12-fold symmetric photonic

quasi-crystal exhibits long-range

further increasing light extraction

order and short-range disorder and

possesses semi-random properties,

What's more, due to its highly

due to total internal reflection).

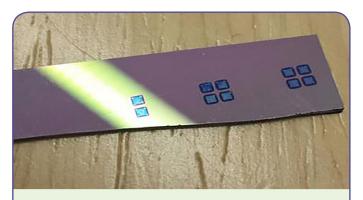

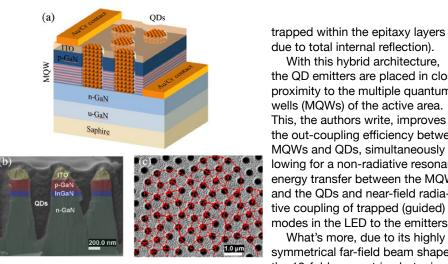

# Quantum dots get deeper into LEDs

By Julien Happich

oasting record-breaking colour conversion effective quantum yields, an international team of researchers has designed a novel photonic quasi-crystal LED structure which deeply embeds quantum dots within the whole stack of the LED's active layers.

The researchers first grew a LED stack of GaN/InGaN Multi-Quantum Well onto a sapphire substrate, and then used nano-imprint lithography and plasma etching to "punch" the whole stack and structure it as a 12-fold symmetric quasi-crystal (PQC).

Forming an array of 480nm radius cvlindrical holes with a lattice pitch of 750nm, the PQC structure was etched deep enough to penetrate through the whole MQW active area, then filled with a blend of quantum dots (QDs) deposited through a spin coating process.

In their Optica paper "Hybrid photonic crystal light-emitting diode renders 123% color conversion effective quantum yield", the researchers see this hybridization and the specific quasi-crystal geometry they chose as key factors.

When used for LED colour conversion, colloidal quantum dots (QDs) are usually dispersed into an encapsulation layer above the active LED structure, missing out the majority of the light emitted by the LED (60% to 80% of which remaining

(a) Schematic representation, (b) crosssectional, and (c) top SEM images of a photonic quasi-crystal LED hybridized with QD color converters.

compared to traditional photonic crystals.

The researchers report effective quantum yields for the QD emitters reaching 123% for single QD species colour converters, and around 110% for a white blend of three commercially available QDs (emitting at 535, 585 and 630nm) achieving a guasi-perfect 6500 K D65 spectrum. They think these performances could be further improved by using state-of-the-art nanocrystalline emitters.

# Solar cell efficiency pushed to 35%

#### By Nick Flaherty

esearchers in Australia have hit a new record for the efficiency of solar cells.

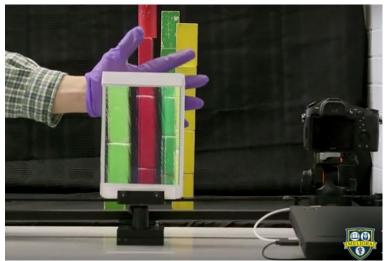

A new solar cell configuration developed by engineers at the University of New South Wales has pushed the efficiency of solar cells to 34.5%, a new world record for unfocused sunliaht.

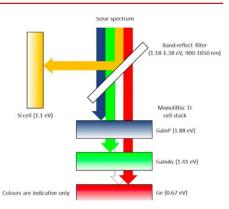

The experimental set up uses a 28cm<sup>2</sup> four-junction minimodule embedded in a prism to extracts the maximum energy from sunlight. It does this by splitting the incoming rays into four bands, using a hybrid four-junction receiver to absorb different frequencies in the separate layers.

The UNSW result, confirmed by the US National Renewable Energy Laboratory, is almost 44% better than the previous record - made by Alta Devices of the USA, which reached 24% efficiency, but over a larger surface area of 800cm<sup>2</sup>.

"This encouraging result shows that there are still advances to come in photovoltaics research to make solar cells even more efficient." said Dr Mark Keevers. Senior Research Fellow of UNSW's Australian Centre for Advanced Photovoltaics. "Extracting more energy from every beam of sunlight is critical to reducing the cost of electricity generated by solar cells as it lowers the investment needed, and delivering payback faster."

A recent study by Germany's Agora Energiewende think tank

set an aggressive target of 35% efficiency by 2050 for a module that uses un-concentrated sunlight, such as the standard ones on family homes.

The triple-junction

cell targets discrete bands of the incoming sunlight, using a combination of three layers: indium-gallium-phosphide; indium-gallium-arsenide; and germanium. As sunlight passes through each layer, energy is extracted by each junction at its most efficient

wavelength, while the unused part of the light passes through to the next layer, and so on. Some of the infrared band of incoming sunlight, unused by the triple-junction cell, is filtered out and bounced onto the silicon cell, thereby extracting just about all of the energy from each beam of sunlight hitting the mini-module.

Scaling the cell up to a larger 800cm<sup>2</sup> is well within reach, says Keevers. "There'll be some marginal loss from interconnection in the scale-up, but we are so far ahead that it's entirely feasible," he said. The theoretical limit for such a four-junction device is thought to be 53%, which puts the UNSW result two-thirds of the way there.

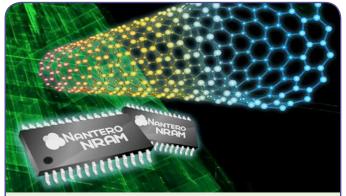

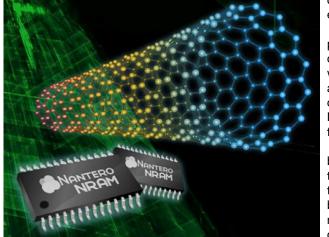

# Nanotube-based NRAMs taking over the world soon, says Nantero

#### By Julien Happich

ounded in 2001, shortly after CTO and Co-Founder Dr. Tom Rueckes had published his seminal Science paper "Carbon Nanotube-Based Nonvolatile Random Access

Memory for Molecular Computing", Nantero is now confident it will take a big chunk out of the \$85+ Billion memory market.

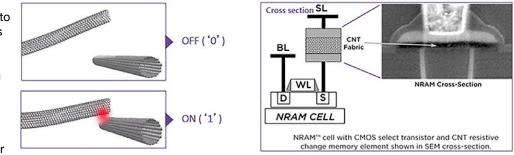

Back in July 2000, the paper was laying the foundations for a bistable non-volatile RAM cell to be designed with a suspended Single Wall Carbon Nano Tubes (SWCNTs) crossbar array, switchable into well-defined Off and On states. The device being designed in such a way that each state represent a potential energy minimum (a balance between elastic energy in the Off state and the van der Waals energy in the On state), switched by charging the nanotubes

to produce attractive or repulsive electrostatic forces.

In his paper describing the 1 transistor SWNT NRAM cell, Rueckes had established possible switching speeds up to 100GHz for a 20nm device, extrapolating this to 200GHz operation for a cell designed at the 5nm node (owing to the smaller effective mass of the moving CNTs). Other claims are that the NRAM operates at orders of magnitude more cycles than flash (over 10<sup>11</sup> program endurance) and retains memory for over 10 years at 300°C (could be over a thousand years at 85°C).

Since then, the startup has secured an extensive patent portfolio (175+ US patents issued and over 200 patent applications pending, including internationally) and boasts a dozen high profile customers lining up to license its IP.

The company expects both foundries and OEMs to license the IP, for some to embed the CMOS-compatible NRAM within chip designs, and for others to produce DDR4-compatible multi-GByte arrays as pure memory chips.

"We want to be the ARM of the memory business", said Greg Schmergel, Nantero's CEO and Co-founder in an interview with *EETimes Europe*.

For practical manufacturing purposes and because today no

For practical manufacturing purposes a lithographic equipment would reach the 2nm level of precision equivalent to a CNT's diameter, the actual switches do not rely on single CNTs but rather on a random mesh of hundreds of CNTs with many different intersection points, explained the CEO.

"Lithography is our main limiting factor, we deposit the carbon nanotubes through a spin coating process before patterning the switches, so our technology can scale pretty much as far as lithography can go" he said.

"For now, we see most design efforts around the 2x nm node, typically 28nm, and our customers achieve densities higher than DRAM" Schmergel said, hinting that the first pro-

duct tape-outs were due for the end of the year.

"We wanted to design 15nm prototypes, but we couldn't access any lithographic equipment with resolutions below 15nm" he added, reminding us that the initial claims of the paper were that the NRAM cells could be built with as few as two nanotubes.

On the upside of having random bundles of carbon nanotubes acting as bulk switches is the fact that the same NRAM device could be run either as a single-level memory (one bit per switch) or on multi-levels (several bits per

switch) providing the appropriate encoding schemes are used.

"It would essentially be the same structure, you would not need to re-engineer the device to move to a multi-level memory device", confirmed Schmergel, adding that for the next few years, the company would focus on single-level memory devices.

So how cost-competitive will these devices be?

"For embedded memory, we have a cost advantage because we use less power than embedded flash, there is also less overhead circuitry and our process only requires one or two mask layers versus many masks for flash" Schmergel says.

The CEO expects NRAM to compete with standalone DRAM in the near term, while it could take longer to beat flash on cost alone. But as customers move to smaller nodes and ramp up their production, then CNT-based memory could end up consolidating the memory marketing, eventually replacing multiple memory chips into one fast nonvolatile memory chip.

The bi-stable CNT switches could also be used as configurable logic tables, Nantero also has IP for sensors, interconnects and loss-less transistors, but is not actively commercializing it for now.

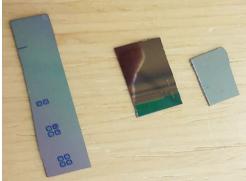

NRAM switch working principle (left) and physical implementation (right).

# **INNOVATE FASTER**

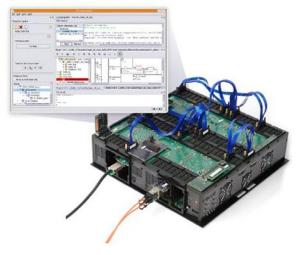

#### WITH FIELD-DEPLOYED 5G PROOF-OF-CONCEPT SYSTEMS

In the race to design next-generation wireless technologies, research teams must rely on platforms and tools that accelerate their productivity. Using the NI software defined radio platform and LabVIEW Communications, leading researchers are innovating faster and building 5G proof-of-concept systems to demonstrate new technologies first.

Accelerate your innovation at ni.com/5g

LabVIEW Communications System Design Software, USRP-2943R SDR Hardware

# **NEWS & TECHNOLOGY**

# **Toward a digitally reconfigurable optical cloak**

#### By Julien Happich

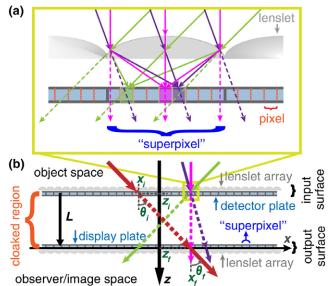

n their recent Optica paper "digital integral cloak", researchers from the University of Rochester combine a scanning camera on one side and an LCD display overlaid with an array of micro-lenses on the other side of the object to be concealed, together with ray-tracing algorithms running in between.

The proof-of-concept demonstration tricks the eyes into seeing what's behind the cloaked object as if the light rays were directly passing through the "invisible" object.

The cloak is reconfigurable in the sense that if the background changes, the output can be updated through another scan of the background area by the camera, with ray-tracing algorithms put into play to compute the right display rendering on the LCD so each micro-lens redi-rects the right colours in the right directions (the maths have to take into account the depth of the concealed zone).

The thin, parallel semi-cylindrical micro-lenses then recreate multiple images of the background, hence perfecting the illusion regardless of the viewer's position (a considerable improvement over a flat 2D rendering which would equate to intercalating a poster of the background).

Because the proof-of-concept experiment only used a camera mounted onto a rail for scanning the background, it took PhD student Joseph Choi and his advisor Professor of Physics John Howell several minutes to scan, pro-cess and update the image on the screen for every change in background.

But in the future, Choi envisages that one side of the object to be concealed could be covered with a lenticular array of optical sensors, and a conformable lenticular display onto its other side showing the right pixels in all directions so as to show the background as if the object weren't there. A fixed setup would only work as long as the object's shape wouldn't change, the geometry and spatial location of the optical sensors being taken into con-sideration in the mathematical model to compute which pixels to feed on the output display.

Pushing the concept further, the author concludes that the surface of the cloak could be discretized with so-called superpixels that could both detect and emit multiple discrete ray positions and angles. Combined with enough computational power, such a digital cloak could function in real-time for just any object shape, allowing for wearable and deformable cloaks. Increasing display resolutions and ever shrinking flexible sensor technologies could turn such an implementation into reality, Choi thinks.

The Rochester Digital Cloak is patent pending and the university is open for business to further its research into a commercial product.

Cross section of a digital integral cloak showing two parallel 2D surfaces, with a few sample rays. The input "surface" (lens array and plate) captures input light rays. The output surface displays rays as if they passed through ambient space only (dashed lines). Superpixels, placed at the focusing plane of a lenslet, collect rays with the same position as the lens. These rays are then spatially separated into pixels, such that one ray angle (or "view") maps to one pixel. Display (output) is the reverse of the detection scheme.

Concept of an ideal spherically symmetric cloak with example rays (solid arrows) entering and exiting the cloak. Dashed arrows show how the rays appear to have traveled inside the cloak (where objects are invisible). Such a cloak would be omnidirectional.

#### WEARABLES

# SkinTrack technology turns arm into touchpad

#### By Jean-Pierre Joosting

the entire lower arm into a touchpad could be a sloultion to the tiny interface presented by smartwatches.

Called SkinTrack and developed by the Human-Computer Interaction Institute's Future Interfaces Group, the system allows for continuous touch tracking on the hands and arms. It also can detect touches at discrete locations on the skin, enabling functionality similar to buttons or slider controls. Previous "skin to screen" approaches have employed flexible

overlays, interactive textiles and projector/camera combinations that can be cumbersome. SkinTrack, by contrast, requires only that the user wear a special ring, which propagates a lowenergy, high-frequency signal through the skin when the finger touches or nears the skin surface.

"The great thing about SkinTrack is that it's not obtrusive; watches and rings are items that people already wear every day," said Yang Zhang, a first-year Ph.D. student in HCII."A major problem with smartwatches and other digital jewelry is that their screens are so tiny." said Gierad Laput, a Ph.D.

a first-year Ph.D. student in HCII."A Carnegie Mellon University's SkinTrack enables users to turn their skin into a other digital jewelry is that their screens are so tiny." soid Gierad Laput a Ph D

student in HCII and part of the research team. "Not only is the interaction area small, but your finger actually blocks much of the screen when you're using it. Input tends to be pretty basic, confined to a few buttons or some directional swipes."

"SkinTrack makes it possible to move interactions from the screen onto the arm, providing much larger interface," said Chris Harrison, assistant professor in the HCII and adviser to the research. The user wears a ring that produces a high-frequency electrical signal. When the finger gets near to the skin or touches the skin, that signal propagates through the skin.

By using electrodes integrated into the watch's strap, it's possible to pinpoint the source of those electromagnetic waves because the phase of the waves will vary. Electrodes corresponding to the 12 o'clock and 6 o'clock positions on the watch, for instance, can detect phase differences that can determine the position of the finger along the width of the arm; electrodes at the 3 o'clock and 9 o'clock positions can determine the finger's position along the length of the arm.

The researchers found that they could determine when the finger was touching the skin with 99 percent accuracy and they could resolve the location of the touches with a mean error of 7.6 millimeters. That compares well with other on-body finger-tracking systems and approaches touchscreen-like accuracy.

The researchers showed that SkinTrack could be used as a game controller, to scroll through lists on the smartwatch, to zoom in and out of onscreen maps, and to draw. A number pad application enabled users to use the back of the hand as a dial pad for the onscreen number pad; hovering a finger over the hand acts as a cursor, highlighting numbers on the screen to aid in targeting touch points. The system has some limitations. Keeping the ring powered up is a challenge. Signals also tend to change as the device is worn for long periods, thanks to factors such as sweat and hydration and the fact the body is in constant motion.

The technology is safe. No evidence suggests that the radio frequency signals used by SkinTrack have any health effects. The body is commonly excited by daily appliances – everything from the tiny amounts of current drawn from the finger by touchscreens to the electromagnetic noise emanating from fluorescent lights – with no ill effects.

# Fujitsu Electronics Europe

"We enable our clients to deliver better products and shorten development cycles. This is how we drive innovation." *Michael Pochmann,* Senior Field Sales Engineer FEEU

### The global gateway to new products and markets

As a Value Added Distributor, we're a partner who understands your challenges. By providing fast access to tailored solutions, we help to accelerate your product development process.

Your benefits:

- Shorter development times and faster time to market

- Proven global supply chain with 35 years of experience

- Perfect adherence to delivery dates and complete reliability

# **NEWS & TECHNOLOGY**

# **Android N joins auto OS battle**

#### By Junko Yoshida

his auto-centric variant of Android N OS—natively running in a car—would allow carmakers to develop infotainment systems that can access heating and air conditioning, AM/FM radio, connectivity and other core functions besides the usual media, navigation and messaging apps.

Google showed off Android N on a reference In-Vehicle Infotainment (IVI) concept system inside a Maserati Ghibli. The system featured a vertical 15-inch screen—much like the one you find in Tesla today—and high-definition digital instrument cluster powered by Qualcomm's Snapdragon 820 chip.

What changed?

Up until now, Google has not offered "autospecific middleware to control infotainment systems," Egil Juliussen, senior director & principal analyst IHS Automotive, told *EE Times*. The lack of a middleware standard has sent car OEMs and Tier Ones scrambling for proprietary middleware or some version of Linux OS for invehicle infotainment systems.

Undoubtedly, Android N will give Google a much deeper inroad into the automotive market. It allows Google to offer automakers a range of apps and services from which to choose.

More important, when Google does this middleware, "it becomes a standard that will be updated by Google," said Juliussen. "It saves the OEMs from doing so."

Ultimately, Google's move will lead to a shakeup of embedded operating systems – especially the growing number of different versions of Linux OS currently proliferating on the automotive market.

IHS predicts Google's move will "consolidate the many Linux OS versions to two—Android N OS and GENIVI-compliant OS (and potentially a Chinese-centric Linux variant, such as YunOS, which is essentially a forked version of Android)."

GENIVI is a Linux-based operating system, middleware and open-source development platform for the automotive in-vehicle infotainment (IVI) industry, grown out of GENIVI Alliance – founded in 2009 by BMW Group, Delphi, GM, Intel, Magneti-Marelli, PSA Peugeot Citroen, Visteon, and Wind River Systems.

Juliussen foresees a future OS battle in the IVI market primarily fought among QNX, GENIVI Linux and Android Linux. Meanwhile, Android N OS will "hasten the phase-out of the auto version of Microsoft Windows Embedded and other proprietary OS products," he added.

But how will QNX—owned by Blackberry—hold up against Android N?

Juliussen observed that QNX is well prepared for an infotainment Android N OS because BlackBerry has developed a software emulation of Android APIs. "This means that QNX can co-exist with Android Auto and Android N OS better than its competitors in most cases," he noted.

However, IHS expects QNX's dominant share in infotainment OS to "decline somewhat by the introduction of Android N." The

research firm predicts that Android N could reach 35 percent globally sometime after 2020.

How close to commercialization?

Today, Android N isn't the final name, and there is no commercial name for the auto-centric variant of Android N, either. But this could quickly change.

IHS pointed out that General Motors and Harman earlier announced a partnership to build Android-based infotainment systems for GM vehicles. "This \$900 million contract will bore a new next-generation infotainment system powered by Android

Android N OS running on screens (of head unit and instrument cluster) inside Maserati Ghibli (Source: Google)

> by the end of 2016—it's possible that those vehicles will be powered by this Android embedded system," said IHS analysts in their research note.

> The Google-designed interface will be offered free to automakers. Most likely, OEMs will develop their own HMI – or skin – over the Android N OS.

> Judging from how Google has changed the smartphone market with Android OS, it could do the same to the IVI market – simply by following the same playbook.

> No one has measured OEMs' enthusiasm or resistance. But Google is counting on its app store and core services to entice carmakers to go with Android N.

Qualcomm gets a foot in the door

Qualcomm has played a key role working with Google to embed the power of the Android OS into the car.

Just as Qualcomm's Snapdragon processors have dominated the Android smartphone market, Qualcomm sees a big opportunity for its auto-grade Snapdragon processors to star in connected cars and infotainment systems.

The concept car functions demonstrated at Google I/O used Qualcomm's Snapdragon 820A integrated with CPU, GPU, X12 LTE modem (capable of Cat 12 speeds) and video processing capabilities.

Qualcomm believes the creation of infotainment systems

#### **IOT EXPANSION**

using Android as a common platform will make it easier for OEMs and Tier Ones "to add connected services and applications, and accelerate innovation in the car." Android Auto

Google developed Android Auto as a smartphone projection standard. It allows mobile devices running the Android OS – connected over USB or Bluetooth – to be projected on the dashboard's head unit and operated in cars.

Now that Android N could do so much more, what will happen to Android Auto? At Google I/O this week, Google announced that Android Auto will work as a standalone app in the car. In short, Google will untether Android Auto from the dashboard, so that an updated Android Auto app can work independently of infotainment systems.

IHS believes that this is a right strategy. It means drivers with older cars or no infotainment systems can simply "mount their phone and still get the benefits of Android Auto," the research firm said.

Such moves "will dramatically increase the potential market of Android Auto app users, and that with the increased potential customer base, many more apps will be announced for Android Auto," according to IHS. "We expect many of those apps will seamlessly work with Android's IVI OS system, too."

# IoT piggybacks on Lego: simple physics

#### By Julien Happich

oing quantum physics research at the Tel Aviv University, Boaz Almog is probably best known for his papers about quantum levitation when together with Barak Deutscher from the superconductivity group at Tel-Aviv University, he demonstrated over fifteen years ago how a superconductor disk can be trapped in a surrounding magnetic field.

Since then, the quantum physicist has been busy educating the masses about superconductivity, both through public demonstrations and more recently by commercializing demonstration kits via his company, Quantum Experience - www.quantum-levitation.com – founded in 2013.

Yet, the CEO started up another company in June last year, Brixo Smart Toys

ity sensors. The conductive bricks feature flexible side-arms that ensure electrical connection between two adjacent blocks, and the whole assemblies are powered by a Bluetooth-controlled 9V battery block. The built-in Bluetooth controller lets users change the current's direction and voltage levels via a mobile application.

That means the Brixo bricks can not only be triggered by sound, light and touch, but also controlled by any Bluetooth connected device, taking the good old Lego bricks further into the IoT world (the Danish company already has its entries in the cloud via its Mindstorms Lego series and the augmented-reality capable Nexo Knights toys).

The company is promising open 3D building instructions, an online library of models and hacks to its followers, encouraging a community of Brixo enthusiasts to share their models.

Itd, with the scope to commercialize Legocompatible electronic bricks. Running a crowdfunding campaign on KickStarter and only with a few hours left, the Israeli startup has raised well over ten times its initial \$50,000 goal, offering what it describes as Lego on steroids.

The chrome-plated bricks can conduct electricity, integrate active parts such as LED lights, motor blocks, and even sound, light and proxim-

#### Datamate

## High-Reliability Connectors

High-Reliability Connectors Resist Shock and Vibration on a 2mm Pitch

- 2mm pitch

- High-reliability / high-performance connector system

- Screw fixings for security of connection

- Mixed-layouts of Power, Signal and Coax

For technical specifications go to:

www.harwin.com/ datamate

# **NEWS & TECHNOLOGY**

# Stretchable polymer optics embed carbon nanotubes for better focus

#### By Julien Happich

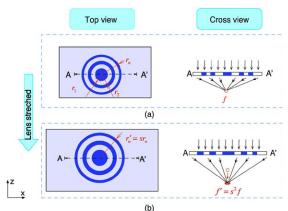

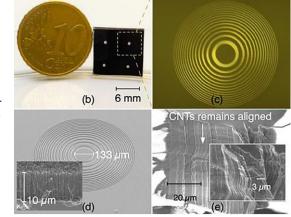

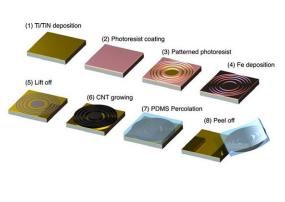

esearchers from the Department of Microelectronics at the Delft University of Technology have flattened out the binary Fresnel lens concept to a thin stretchable polymer membrane with radial patterns of vertically grown carbon nanotubes (CNT). The integration of CNTs, grown perpendicular to the optical plane, ensures a very high optical absorption (a transmittance of only 0.06% in the visible light spectrum versus the 93.9% transmittance of the PDMS membrane), hence a very good contrast to spatially modulate the intensity distribution of the light passing through the diffraction patterns of the binary Fresnel lens.

The carbon nanotubes are grown in concentric rings only 10µm high, before being percolated with polydimethylsiloxane and being peeled off with the stretchable membrane. This makes such diffractive optics only a few tens of micron thick.

In their paper "Stretchable Binary Fresnel Lens for Focus Tuning", the researchers report their results using lenses that are 6×6mm square with a focal length tuneable from 7mm to about 9mm by radially stretching the lens a few percent of elongation. Although they experienced some distortion due to the clamping system they used to stretch the lens, an integrated circular actuator could certainly solve the issue, providing a uniform radial deformation.

Lead author Xueming Li is keen to highlight that although the paper only mentions a 7mm focal length, the researchers worked on other focal lengths.

"Using the same concept and fabrication process, we fabricated lenses with focal lengths ranging from 100µm to 20mm, so to match application specific demands.

When stretching the flexible substrate radially by s from (a) to (b), the radius of the n<sup>th</sup> zone increases from  $r_n$  to  $r'_n$  and the focal length changes from f to f' by a factor of  $s^2$ .

(b) A fabricated device containing 2×2 lens units, with each unit 6×6mm<sup>2</sup> in size. (b) An optical microscopy image of a single lens and (c) a SEM image of a single lens unit, with 7mm in focal length and an innermost zone diameter of 133µm, before PDMS infiltration. (e) shows the CNT inside the PDMS well aligned after the PDMS percolation forming the CNT/PDMS composite.

For instance, a focal length ranging from 5µm to 8.5mm can be used in microscopy to investigate fluorescence signals. Lens arrays with focal length ranging from 2mm to 20mm can be used for compound eye applications and point of care devices" Li wrote *EETimes Europe*.

"Due to the controllable variable focal length, this configuration can also be applied to multi-focus contact lens applications" he added.

Referring to competing research performed with less adaptive rigid materials such as black silicon for the opaque material instead of CNTs, Li notes: "The advantages of using CNTs are first, the porous character of the layer, which allows the PDMS to better penetrate in the CNTs. This is important for radial control when stretching the lens. Secondly, the fabrication of CNTs is more controllable than black silicon, which makes it a more reliable process for large scale device manufacturing. The fabrication of our lens (array), of which the key process is the growth of patterned CNTs, is fast and reliable. Moreover, as a commercially available CVD system is used, and a wafer scale process is developed, it is possible to scale up the area for large volume manufacturing of these devices".

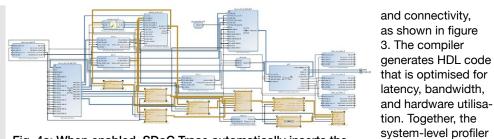

Li sees such flat optics find their way into miniaturized photonic chips, integrated optics, optical interconnects, beam focusing or maskless lithography systems, but also for deflecting and collimating tasks in optical sensor systems or for optical data transfers.